# LASER INTERFEROMETER GRAVITATIONAL WAVE OBSERVATORY

-LIGO-

## CALIFORNIA INSTITUTE OF TECHNOLOGY MASSACHUSETTS INSTITUTE OF TECHNOLOGY

| Document Type                                    | DCC Number       | DCC Number Date |  |

|--------------------------------------------------|------------------|-----------------|--|

| Test Procedure and Results                       | LIGO-T1200365-v2 | 18 August, 2009 |  |

| aLIGO HEPI Pier Interface Chassis Test Procedure |                  |                 |  |

| Ben Abbott                                       |                  |                 |  |

Distribution of this draft: NSF reviewers, LIGO scientists This is an internal working note of the LIGO Laboratory

California Institute of Technology LIGO Project – MS 18-33 Pasadena, CA 91125

Phone (626) 395-2129 Fax (626) 304-9834 E-mail: info@ligo.caltech.edu Massachusetts Institute of Technology LIGO Project – MS 20B-145 Cambridge, MA 01239

> Phone (617) 253-4824 Fax (617) 253-7014 E-mail: info@ligo.mit.edu

www: http://www.ligo.caltech.edu/

#### LIGO-T1200365-v2

| Performed by:          |  |

|------------------------|--|

| Date:                  |  |

| Board Serial Number: _ |  |

#### 1. Overview

The HEPI Pier Interface Chassis serves several functions close to the vacuum envelope. One is to pass through and parse out the hydraulic valve actuation channels. A second function is to read out the L4C Seismometer channels, amplify them, and send them differentially to the Anti-Alias Chassis. Its last function is to read in the Inductive Position Sensor signals, whiten them, and send them differentially to the Anti-Alias Chassis.

The function of this procedure is to check each channel from its input to the respective output and to verify proper DC power consumption.

## 2. Test Equipment

- **2.1** Power Supply capable of +/- 18 volts

- **2.2** Function generator (Stanford Research DS360 or the like)

- **2.3** Oscilloscope

- 2.4 Stanford Research SR785 Network Analyzer, or the like

#### 3. Preliminaries

- **3.1** Perform visual inspection on board to check for missing components or solder deficiencies

- **3.2** Before connecting the power to the chassis, set power supplies to +/- 18 Volts, and then turn them off. Connect the power supplies to the chassis under test at the back panel 3-pin power connector labeled "Power In".

#### 4. DC Tests

**4.1** Turn on the power supplies to the system under test and record the total current.

| Measure     | Voltage read    |   | Current       |

|-------------|-----------------|---|---------------|

| +18V Supply | TP4             | V | 95mA +/- 10mA |

|             | (+15V +/- 0.5)  |   |               |

| -18V Supply | TP5             | V | 95mA +/- 10mA |

|             | (-15V +/- 0.5)  |   |               |

| Power LEDs  | Equally bright? |   | N/A           |

| IPS Power+  | J10-1 / J10-3   | V | N/A           |

|             | (-15V +/- 0.5)  |   |               |

| IPS Power-  | J10-2 / J10-3   | V | N/A           |

|             | (-15V +/- 0.5)  |   |               |

#### LIGO-T1200365-v2

## 5. Dynamic Tests

**5.1 Valve throughput check:** Set a function generator to a **5V** p-p sine wave. Split this signal with a BNC Tee, with one signal going to the designated pins below, and the other going to channel 2 of an oscilloscope. Observe the amplitude at the designated output pins. All of the outputs should be the same amplitude as the input, with no observable phase delay or high-frequency noise. Place a check in the correct cell if the signal looks correct.

| Input               | Output                       |  |

|---------------------|------------------------------|--|

| (Valve Input)       | (Valve1 Out) or (Valve2 Out) |  |

| J8-1 (+) / J8-6 (-) | J9T-1 (+) / J9T-6 (-)        |  |

| J8-2 (+) / J8-7 (-) | J9T-1 (+) / J9T-6 (-)        |  |

| J8-3 (+) / J8-8 (-) | J9B-1 (+) / J9B-6 (-)        |  |

| J8-4 (+) / J8-9 (-) | J9B-1 (+) / J9B-6 (-)        |  |

**5.2 L4C Seismometer Channel Check:** Set a function generator to a **0.05V** p-p sine wave. Input the signal on the correct pins below, and observe the amplitude at the designated output pins differentially (A-B) relative to ground. The outputs should have a gain of 334 V/V.

| INPUT<br>L4C INPUT | OUTPUT<br>TO AA CHASSIS       | VALUE<br>NOM 16.7V |

|--------------------|-------------------------------|--------------------|

|                    | $(\mathbf{A}) - (\mathbf{B})$ | +/- <b>0.5V</b>    |

| L4C Horiz. In      | To AA Chassis                 |                    |

| J1T-1 / J1T-6      | (J4-1/GND) - (J4-9/GND)       |                    |

| L4C Vert. In       | To AA Chassis                 |                    |

| J1B-1 / J1B-6      | (J4-2/GND) - (J4-10/GND)      |                    |

| L4C Wit. In        | To AA Chassis                 |                    |

| J5-1 / J5-6        | (J4-3/GND) - (J4-11/GND)      |                    |

### **5.3 L4C Channel Noise Tests**

To test the noise of the position sensor channels, ground the appropriate pins on the input connector, and do a noise measurement from 0 to 100Hz on the output connector pins specified below. Read the noise at 1Hz and 10Hz. The observed numbers should be below the specification to pass this test.

| L4C            | Ground        | To Rack             | Noise @1                         | Noise @10Hz      |

|----------------|---------------|---------------------|----------------------------------|------------------|

|                | the following | connector J4        | Hz<br>Nominal is                 | Nominal is under |

|                |               |                     | under                            | 75nV/√Hz         |

|                |               |                     | $100 \text{nV}/\sqrt{\text{Hz}}$ |                  |

| L4C Horizontal | L4C Horiz. In | Pins 1(+) and 20(-) |                                  |                  |

|                | J1T-1 / J1T-6 |                     |                                  |                  |

| L4C Vertical   | L4C Vert. In  | Pins 2(+) and 21(-) |                                  |                  |

|                | J1B-1 / J1B-6 |                     |                                  |                  |

| L4C Witness    | L4C Wit. In   | Pins 3(+) and 22(-) |                                  |                  |

|                | J5-1 / J5-6   |                     |                                  |                  |

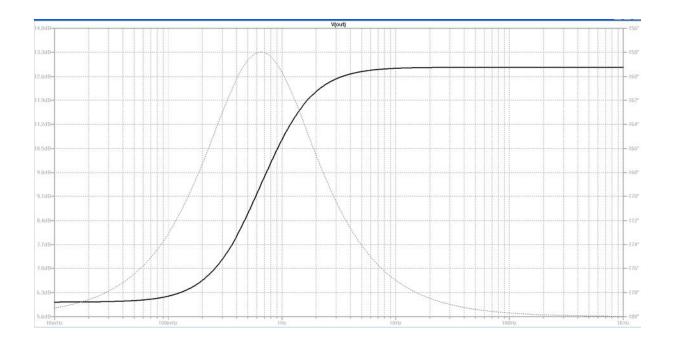

**5.4 Inductive Position Sensor Channel Check:** Set the SR785 for a 100mV source, and do a Swept Sine measurement from 10mHz to 10KHz on each channel. The nominal response is a Zero at 0.38Hz, and a pole at 0.86Hz. This should result in a gain change from 4 V/V at DC to 9 V/V at higher frequencies. The plot should look similar to the graph below.

| INPUT          | OUTPUT                        | VALUE         |

|----------------|-------------------------------|---------------|

| IPS INPUT      | TO AA CHASSIS                 | LOOK LIKE THE |

| (DIFFERENTIAL) | $(\mathbf{A}) - (\mathbf{B})$ | GRAPH?        |

| IPS X In       | To AA Chassis                 |               |

| J10-4 / J10-5  | (J4-4/GND) - (J4-12/GND)      |               |

| IPSY In        | To AA Chassis                 |               |

| J10-6 / J1B-7  | (J4-5/GND) - (J4-13/GND)      |               |

## **5.5 Position Sensor Channel Noise Tests**

To test the noise of the position sensor channels, ground the appropriate pins on the input connector, and do a noise measurement from 0 to 100Hz on the output connector pins specified below. Read the noise at 1Hz and 10Hz. The observed numbers should be below the specification to pass this test.

| <b>Position Sensor</b> | Ground<br>the | To Rack connector J4 | Noise @1 Hz<br>Nominal is | Noise @10Hz<br>Nominal is |

|------------------------|---------------|----------------------|---------------------------|---------------------------|

|                        | following     |                      | under                     | under                     |

|                        |               |                      | 160nV/√Hz                 | 120nV/√Hz                 |

| IPS X                  | IPS X In      | To AA Chassis        |                           |                           |

|                        | J10-4 / J10-5 | (J4-4/GND) –         |                           |                           |

|                        |               | (J4-12/GND)          |                           |                           |

| IPS Y                  | IPSY In       | To AA Chassis        |                           |                           |

|                        | J10-6 / J10-7 | (J4-5/GND) –         |                           |                           |

|                        |               | (J4-13/GND)          |                           |                           |